Actualidad informática

Noticias y novedades sobre informática

Evolución de los microprocesadores Intel

La Universidad de Stanford ha elaborado una base de datos de los microprocesadores que se han comercializado desde 1970 hasta ahora; para cada microprocesador se ha redactado una ficha bastante completa, lo que permite comparar diferentes modelos y ver como han evolucionado la tecnología a lo largo de los años.

| Modelo | Año | Transistores | Tran./mm2 | Watios |

| Procesadores de 8 bits, era previa al PC | ||||

| 4004 | 1971 | 2.300 | 192 | 0,5 |

| 8008 | 1972 | 3.500 | 219 | 1,0 |

| 8080 | 1974 | 6.000 | 300 | 0,8 |

| Procesadores de PC de 16 bits | ||||

| 8086 | 1979 | 29.000 | 879 | 1,7 |

| 80286 | 1982 | 134.000 | 2.851 | 3,3 |

| Procesadores de PC de 32 bits | ||||

| 80386DX | 1986 | 275.000 | 2.670 | 1,7 |

| 80486DX | 1989 | 1.200.000 | 14.815 | 3,0 |

| Pentium | 1993 | 3.200.000 | 10.884 | 13,0 |

| Pentium II | 1997 | 7.500.000 | 36.946 | 12,0 |

| Pentium III | 1999 | 28.000.000 | 264.151 | 16,0 |

| Pentium 4 | 2000 | 42.000.000 | 193.548 | 52,0 |

| Pentium 4 P. | 2004 | 169.000.000 | 1.251.852 | 115,0 |

| Procesadores de PC de 2 núcleos | ||||

| Core 2 Duo | 2006 | 291.000.000 | 2.034.965 | 65,0 |

| Procesadores de PC de 4 núcleos | ||||

| Core i7 N. | 2008 | 774.000.000 | 2.614.865 | 45,0 |

| Core i7 S. B. | 2011 | 995.000.000 | 4.606.481 | 95,0 |

| Procesador de PC de 6 núcleos | ||||

| Core i7 980X | 2011 | 1.170.000.000 | 4.717.742 | 130,0 |

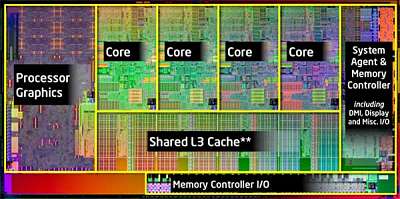

Chips operando como mini-internet

Los chips han dejado de ser cada vez más rápidos. A fin de mantener el aumento del potencia de los chips de computación a la tasa a la que nos hemos acostumbrado, los fabricantes de chips están dando lugar a otros «núcleos» o unidades de procesamiento.

Actualmente, un chip típico puede tener seis u ocho núcleos, todos comunican entre sí sobre un solo haz de «cables», llamado bus. Con un bus, sin embargo, sólo un par de núcleos pueden comunicarse a la vez, lo que sería una grave limitación en chips con cientos o incluso miles de núcleos, que muchos ingenieros eléctricos imaginan como el futuro de la computación.

Li-Shiuan Pe, profesor asociado de ingeniería eléctrica y ciencias de la computación en el MIT (EE.UU.), quiere que los núcleos de de los ordenadores entren en comunicación de la misma manera que opera internet, haciendo lo siguiente: «paquetes» para transmitir la información, cada núcleo tendrá su propio router, que podría enviar un paquete por cualquiera de varios caminos, dependiendo de la condición de la red como un todo.

En la Conferencia de automatización de diseño en junio, Pe y sus colegas presentarán un documento que describe como «resumen 10 años de investigación» en estas «redes en chips.» No sólo los investigadores establecen límites teóricos de la eficiencia de la conmutación de paquetes de –chip– redes de comunicación, pero también las mediciones actuales realizadas en un chip de prueba en la que estuvo muy cerca de llegar a varios de esos límites.

La última parada para los buses

En principio, los chips de varios núcleos son más rápidos que los chips de un solo núcleo, ya que pueden dividirse las tareas computacionales y ejecutarlas en varios núcleos a la vez. Los núcleos de trabajo en la misma tarea en ocasiones tendrán que compartir los datos, pero hasta hace poco, el recuento de núcleos en los chips comerciales ha sido suficientemente bajo para que un solo bus fuera capaz de manejar la carga de comunicaciones adicional. Eso ya está cambiando, sin embargo: «Los buses han llegado a un límite», dice Pe. «Por lo general se escala a cerca de ocho núcleos.» Los chips de 10 núcleos que se encuentran en servidores de gama alta con frecuencia añaden un segundo bus, pero ese método no funciona para chips con cientos de núcleos.

Por un lado, Pe, dice, «los buses consumen mucha potencia, porque están tratando de manejar ocho o 10 núcleos, al mismo tiempo.» En el tipo de red Pe propone, por el contrario, que cada central se comunica sólo con los cuatro núcleos más cercanos a él. «Aquí, usted está conduciendo a través de segmentos cortos de «cables», lo que les permite ir por debajo de la tensión», explica.

Con visión de futuro

Pe y sus colegas han desarrollado dos técnicas para hacer frente a estas preocupaciones. Una de ellas es algo que llaman «bifurcación virtual» (virtual bypassing). En internet, cuando un paquete llega a un router, el router inspecciona la información de direccionamiento antes de decidir cuál es el camino para circular. Con enrutado virtual, sin embargo, cada router envía una señal de avance a la siguiente, de manera que puede predeterminar el interruptor, lo que acelera el paquete sin ningún cálculo adicional. En los chips de prueba de su grupo, dice Pe, permiten un enfoque muy cercano al máximo de transmisión de datos, sobre las tasas predichas por el análisis teórico.

La otra técnica es algo que se llama «señalización de baja oscilación» (low-swing signaling). Los datos digitales se componen de unos y ceros que se transmiten a través de canales de comunicación como tensión alta y baja. Sunghyun Park, un estudiante de doctorado asesorado por Pe y Chandrakasan Anantha, F. José y Nancy P. Keithley profesor de Ingeniería Eléctrica, ha desarrollado un circuito que reduce la oscilación entre las tensiones altas y bajas de un voltio hasta 300 milivoltios. Con la combinación de señalización virtual, pasando por alto y bajo, el chip de ensayo de los investigadores consumía energía un 38 por ciento menos que los anteriores chips de prueba de conmutación de paquetes. Los investigadores tienen mucho trabajo por hacer, dice Pe, el consumo de potencia del chip de prueba se pone tan cerca del límite teórico como su velocidad de transmisión de datos lo hace. Pero, añade, «si lo comparamos contra un bus, tenemos varios órdenes de magnitud de ahorro».

Luca Carloni, profesor asociado de ciencias informáticas en la Universidad de Columbia, que también investiga las redes en el chip, dice que «el jurado está todavía fuera», sobre el futuro del diseño de chips, pero que «las ventajas de las redes de conmutación de paquetes de chips parecen convincentes». Se hace hincapié en que esas ventajas incluyen no sólo la eficiencia operativa de los chips mismos, sino también» un nivel de regularidad y productividad en tiempo de diseño que es muy importante. «Y en el campo, añade,» las contribuciones de Li-Shiuan son fundamentales. »

Esta historia se publica por cortesía de las noticias del MIT (http://web.mit.edu/newsoffice/ ), un sitio popular que cubre las noticias sobre la investigación del MIT, la innovación y la enseñanza.

Microprocesadores de ordenador: ahorro de energía y dinero

En los microprocesadores de hoy en día, gran parte de la potencia consumida para poner en funcionamiento el procesador se está desperdiciando.

A un equipo de investigadores de Case Western Reserve University, se le ocurrió una idea novedosa llamada puerta de potencia de grano fino, lo que ahorra energía y dinero en un par de maneras: se utiliza menos energía y menos calor.

«El uso de menos energía produce menos calor. Menos calor significa que se necesita menos enfriamiento», dijo Swarup Bhunia, profesor de ingeniería eléctrica y ciencias de la computación y un autor de la investigación. «Eso puede evitar la necesidad de un ventilador grande para enfriar el procesador, lo que ahorra mucho dinero». Los procesadores se utilizan en una variedad de productos, desde computadoras hasta teléfonos celulares. Los gastos operacionales podrían reducirse en más de un tercio, dicen los investigadores.

Bhunia, Lei Wang y Somnath Paul, cuyo trabajo fue financiado por la Corporación Intel, presentaron su idea en la 25 ª Conferencia Internacional sobre la VLSI (Very-Large-Scale Integration) de diseño. Recibieron el premio a la mejor ponencia en la conferencia, celebrada en Hyderabad, India.

Bhunia explicó que dos partes de un procesador consumen energía: la ruta de datos y la memoria. La ruta de datos realiza cálculos y toma decisiones de control, mientras que almacena los datos de la memoria. En informática rara vez se requiere todo lo que un procesador es capaz de proporcionar durante todo el tiempo, pero todo el procesador está totalmente encendido de la misma manera.

Un intento de mejorar la disipación de potencia en los procesadores es a través de algo llamado coarse gating. Se apaga un bloque completo del procesador que no está siendo utilizado. Por ejemplo, habitualmente el bloque que realiza las sumas consume energía aunque no esté el microprocesador efectuando una suma.

El problema con este método es que la mayor parte del tiempo encontrar un bloque completo que no está siendo utilizado en un momento dado es dura.

El equipo de la Case Western Reserve tuvo la idea de compuerta para apagar sólo las partes de un componente que no se están utilizando en ese momento. La memoria funciona del mismo modo. Un procesador tiene que ser capaz de almacenar grandes cantidades, pero rara vez en realidad las almacena.

Esto puede no parecer mucho, pero añade todo y se hace una gran diferencia. El equipo calculó que el ahorro de energía total de un procesador típico de un sistema de alto rendimiento, tales como una computadora de escritorio, sería de alrededor de 40%.

Bhunia explicó que su sistema no puede ser aplicado a los procesadores actuales, pero podrían ser utilizados por las empresas para construir procesadores de próxima generación. Este nuevo método no sólo ayuda a las corporaciones sin embargo, pues una batería de teléfono móvil celular, pasaría de durar ocho horas a 11, por ejemplo.

Fuente: Case Western Reserve University, via Newswise.

Robert Noyce, inventor del circuito integrado es el homenajeado por Google en su doodle

En el buscador de Google aparece hoy un chip que forma su doodle y pulsándolo conduce hasta la página donde se muestra información relacionada. Hoy Google rinde homenaje con este doodle en forma de microchip al creador de este tipo de elemento, Robert Noyce, que actualmente es la base de casi todos los .dispositivos que se usan en cualquier ámbito de la actividad humana El reconocimiento de este invento se dio tanto a Robert Noyce como a Jack Clair Kilby.

Robert Noyce además fue cofundador de la empresa Intel fabricante de microprocesadores habituales en los ordenadores y que son el núcleo de estas máquinas. Hoy 12 de diciembre se cumplen 84 años desde el nacimiento de este científico que falleció a los 62 el año 1990.

El primero de estos microchips llegó al mundo en 1961 y en año 1964 algunos de estos microprocesadores ya contaban con 32 transistores, que parecen ridículo si los comparamos con los más de 700 millones que poseen los últimos Intel Core i7.

Estos datos también nos sirven para darnos cuenta de la gran evolución que ha sufrido la tecnología en este último medio siglo.

Fuente: es.wikipedia.org

Intel e IBM revelan el futuro de los «chips» para ordenadores

En las últimas horas hemos visto a dos de los nombres más importantes en la tecnología de revelando el futuro de los chips para computadoras -ya sea intencionalmente o no.

Un documento filtrado de Intel muestra que la pautade compañía la para la siguiente generación de procesadores, que debe comenzar a rodar a principios del año que viene. Mientras tanto, IBM ha presentado su visión a largo plazo de la tecnología de procesamiento, comienza a trazar los desarrollos sin descubrir lo que viene después de silicio cuando se vuelva obsoleto. La compañía ha mostrado algunas de estas técnicas emergentes, que a menudo superan a sus equivalentes de silicio y se puede construir utilizando técnicas de producción similares.

La llegada de Ivy

En un documento filtrado reportados por X-bit Labs , Intel revela su hoja de ruta de productos para Ivy Bridge, la nueva generación de chips de computadora que se encontrará pronto en PCs y Macs. Ivy Bridge lleva a la compañía al rango de 22 nanómetros en los microprocesadores. Los chips más pequeños logran mayor frecuencia de procesamiento.

Ivy Bridge sinifica máquinas con cerca de 4 GHz de potencia de procesamiento, de acuerdo con el documento Top-of-the-line, el Intel Core i7 3.9 GHz contará con un diseño de cuatro núcleos, lo que significa que las distintas partes del chip puede trabajar de forma independiente. Esto es útil en software, como juegos, que pueden tener múltiples operaciones a la vez. El chip más bajo de gama, un diseño de Core i5, seguirá siendo de cuatro núcleos funcionando a 2,7 GHz, siendo bastante rápido para los estándares actuales.

Aunque estos chips utilizan una nueva tecnología conocida como Tri-Gate, todavía están basados en el silicio. El cofundador de Intel Gordon Moore escribió la célebre frase acerca de cómo el número de transistores en los chips de silicio se duplicaría aproximadamente cada dos años, y la tecnología en general ha seguido ese paso. Es tan consistente que la observación se conoce como Ley de Moore.

Mientras los fabricantes de chips están todavía investigando las profundidades a las que llegan en términos de mantener el número de transistores cada vez más reducidos, se llegará a ese límite muy pronto, dicen los expertos. Una vez que los circuitos se reduzcan a alrededor de siete nanómetros, los efectos cuánticos empiezan a suceder, y será imposible lograr chips más pequeños – no con silicio, de todos modos.

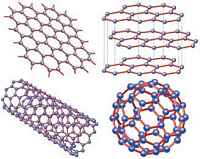

Más allá de silicio

Mientras tanto, IBM presentó su plan a largo plazo, como se informó en el Wall Street Journal , para ir más allá de silicio y la toma del poder de procesamiento a nuevos niveles. La compañía está apostando en tres tecnologías: los nanotubos de carbono, el grafeno, y algo que llama «memoria de circuito.»

El primer enfoque implica el cambio de silicio en favor de carbono. IBM describe cómo la compañía ha construido un transistor hecho de nanotubos de carbono en el rango de 10 nanómetros. Además del pequeño tamaño atractivo, superó al silicio en varias métricas clave.

El grafeno, descubierto en 2004, ha sido aclamado como un nuevo tipo de sustancia se preguntan – a pesar de que es esencialmente una forma de carbono y, al igual que la punta del lápiz. El grafeno es el rey de lo pequeño – tiene sólo un átomo de espesor – y es altamente conductor. IBM construyó el primer circuito de grafeno a principios de este año, y ahora dice que se pueden construir chips de grafeno utilizando las líneas de producción por lo general utilizados para el silicio, que es un buen augurio para la producción masiva.

La memoria de circuito consiste en reemplazar la memoria flash, usado en todo desde iPhones a las tarjetas SD, con imanes microscópicos cambiado a lo largo de alambre pequeño bucles llamados nanocables. IBM ha demostrado esta técnica, también, que también se construye conlas líneas defabricación de productos normales.

La necesidad de velocidad

¿Crees que tu equipo es lo suficientemente rápido? Eso está muy bien, pero hay un montón de aplicaciones para las tecnologías emergentes que están deseando más avances en potencia de procesamiento. Los juegos como Call of Duty: Modern Warfare 3 empujan las máquinas de hoy a sus límites, y la visión de los desarrolladores sólo está limitado por la potencia de procesamiento de las máquinas.

Además, el campo entero de la computación cuántica y hypercomputing dependen de la toma de potencia de procesamiento a niveles hasta ahora desconocidos. La propia IBM tiene grandes planes para las nuevas plataformas que surgen de su muy publicitado proyecto Watson , y aquellos que necesitan la potencia de procesamiento avanzadas.

Mientras que el futuro de las computadoras es todavía incierto, en definitiva, los fabricantes de chips están trabajando frenéticamente para asegurarse de que no llegan a un punto muerto.

Fuente: mashable Tech

Ordenador de doble núcleo en una llave electrónica

La empresa noruega FXI technologies mostró un prototipo de memoria USB del tamaño de una llave electrónica (pendrive), con una CPU de núcleo doble a 1.2 GHz ARM de Samsung Exynos (igual que en el teléfono móvil celular Galaxy S II), Wi-Fi 802.11n, Bluetooth, HDMI- y una ranura para tarjetas microSD para memoria. Con nombre en código Cotton Candy (dulce de algodón) por sus 21 gramos, el PC permite lo que su inventor denomina «Cualquier Informática de la pantalla,» la capacidad de convertir cualquier televisor, ordenador portátil, teléfono, tableta en un terminal «tonto» de su sistema operativo Android.

Tiene un conector USB 2.0 en un extremo y un conector HDMI en el otro. Cuando se conecta a una televisión de alta definición, utiliza el puerto HDMI para vídeo, el cable USB para la alimentación eléctrica, y Bluetooth para conectarse a un teclado, un ratón o tableta, para controlar el sistema operativo. El dispositivo admite una resolución de hasta 1080 p por lo que incluso una pantalla Full HD puede mostrar el sistema operativo preinstalado en su resolución nativa el Candy Android 2.3. La CPU de doble núcleo es lo suficientemente potente como para reproducir vídeo a 1080 p y vídeos de alta definición desde la web. Obtenga más información en el vídeo a continuación.

Ampliar información en: FXI Technologies/a>

Avances en la computación paralela

El paralelismo es una forma de computación basada en un principio aparentemente simple: dividir los problemas grandes en varios pequeños y solucionarlos simultáneamente, lo que permite ejecutar más instrucciones en menos tiempo. Pero llevado a la práctica es una cuestión compleja en la que se encuentran investigando grupos científicos de todo el mundo.

“El problema que pretendemos resolver es que los ordenadores de hoy en día han dejado de ser cada vez más rápidos y, los fabricantes, en vez de hacer un único microprocesador más avanzado, que tiene unos consumos muy elevados, lo que hacen es poner dos, cuatro o más, incluso 80 en algunos ordenadores experimentales”, detallan los investigadores Diego Llanos y Arturo González (Universidad de Valladolid). Esto ha sido posible gracias a una mejora en la tecnología de fabricación, que ha posibilitado una reducción en el tamaño de los elementos que componen estos microprocesadores y, por tanto, que se puedan incluir más dispositivos en la misma área.

“En lugar de introducir un microprocesador se colocan varios, juntos, para consumir menos. El problema es cómo sacarle partido a varios núcleos, ya que los microprocesadores funcionan de manera secuencial, es decir, si tienen que ejecutar un único programa y con un núcleo alcanza, el resto no hace nada”, explican.

Se trata, pues, de una “cuestión de eficiencia”. “Nosotros trabajamos en paralelización de algoritmos. Aprovechar dos núcleos es posible, pero cuando se habla de 4, 8, 16, etc, si se tiene una sola aplicación de cálculo intensivo, la cuestión es cómo aprovecharlos, es decir, qué hacer para que realmente funcionen todos a la vez”, subrayan. La resolución de este problema ocupa a la comunidad científica internacional, que está intentado obtener “una versión paralela que distribuya la tarea entre todos los obreros y por tanto aprovechar de forma automática un programa que ahora es secuencial, que primero hace una tarea y luego otra”.

Ampliar información en: sinc

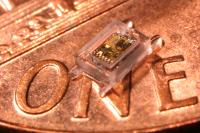

Nuevas tecnologías dan lugar a ordenadores a escala milimétrica

Un prototipo de monitor de la presión ocular implantable para pacientes con glaucoma se cree que contiene en unos milímetros un sistema de computación a escala completa.

Y una radio compacta que no requiera ajuste para sintonizar la frecuencia correcta puede ser un factor clave para la organización a escala milimétrica de los sistemas de redes de sensores inalámbricos. Estas redes podrían un día rastrear la contaminación, monitorear la integridad estructural, realizar la vigilancia, o hacer prácticamente cualquier objeto inteligente y rastreable.

Ambos desarrollos en la Universidad de Michigan (EE.UU.), son hitos importantes en la marcha hacia la informática a escala milimétrica, se cree que es la frontera electrónica que viene.

Los investigadores presentarán ponencias sobre cada uno en la International Solid-State Circuits Conference (ISSCC) de San Francisco. El trabajo está dirigido por tres profesores del Departamento de Ingeniería Eléctrica y Ciencias de la Computación: profesores Dennis Sylvester y David Blaauw, y profesor asistente de David Wentzloff.

Ley de Bell y la promesa de la computación ubicua

Casi invisibles a escala milimétrica estos sistemas podrían permitir la computación ubicua, y los investigadores dicen que es el futuro de la industria. Apuntan a la Ley de Bell, un corolario de la Ley de Moore. (Moore dice que el número de transistores en un circuito integrado se duplica cada dos años, doblando la potencia de procesamiento).

La ley de Bell dice que hay una nueva clase de pequeños, ordenadores más baratos cada década. Con cada nueva clase, el volumen se reduce en dos órdenes de magnitud y el número de sistemas por persona aumenta. La ley se ha mantenido desde 1960 mainframes, en los años 80 los ordenadores personales, ordenadores portátiles en los años 90 y actualmente los teléfonos inteligentes del nuevo milenio.

«Cuando se hacen más pequeños que los dispositivos de mano, se llega a estos dispositivos de control», dijo Blaauw. «El siguiente gran desafío es lograr a escala milimétrica sistemas, que ofrezcan una serie de nuevas aplicaciones para el control de nuestros cuerpos, nuestro ambiente y nuestros edificios. Debido a que son tan pequeños, se podrían fabricar cientos de miles en una oblea. Se podrían utilizar cientos de ellos por persona y es este aumento per cápita el que impulsará el crecimiento de la industria de los semiconductores «.

El primer sistema complet0 a escala milimétrica

El nuevo sistema Blaauw y Sylvester está dirigido a aplicaciones médicas. El trabajo que presentaron en ISSCC se centra en un monitor de presión diseñado para ser implantado en el ojo, para hacer un seguimiento convenientemente y continuamente del progreso del glaucoma, una enfermedad que puede producir ceguera. (El dispositivo se espera que esté disponible en el mercado en pocos años).

En un paquete de un poco más de un milímetro cúbico, el sistema incorpora un ultra bajo consumo de energía del microprocesador, un sensor de presión, la memoria, una batería de película delgada, una celda solar y una radio inalámbrica con una antena que puede transmitir datos a un lector externo, el dispositivo que se ubicará cerca del ojo.

«Esta es el primer sistema de computación completo a escala auténticamente milimétrica», dijo Sylvester. «Nuestro trabajo es único en el sentido de que estamos pensando en sistemas completos en los que todos los componentes son de bajo consumo y su ajuste en el chip. Podemos obtener información, almacenarla y transmitirla. Las solicitudes de sistemas de este tamaño son innumerables «.

El procesador del monitor de la presión del ojo es la tercera generación de chips de los investigadores de Phoenix, utiliza una arquitectura de energía única y un modo de reposo extremo, para lograr ultra bajo consumo de energía. El sistema se activa cada 15 minutos para tomar medidas y consume una media de 5,3 nanovatios. Para mantener la batería cargada, se requiere la exposición a 10 horas de luz interior cada día o 1,5 horas de luz solar. Es capaz de almacenar hasta una semana de información.

Si bien este sistema es minúsculo y completo, su radio puede hablar con otros dispositivos como él. Esa es una característica importante para cualquier sistema dirigido a redes de sensores inalámbricos.

Una radio compacta única para permitir las redes de sensores inalámbricos

Wentzloff y el estudiante de doctorado Huang Kuo-Ken han dado un paso hacia permitir tales comunicaciones de nodo a nodo. Han desarrollado una radio consolidada con una antena en el chip que no necesita el adaptador voluminoso que usan los ingenieros cuando dos dispositivos aislados necesitan «hablar» unos con otros.

Han dado lugar a una nueva antena para medir el tiempo por sí misma y actuar como su propia referencia. Mediante la integración de la antena a través de un avanzado proceso CMOS, se puede controlar con precisión su forma y tamaño y por lo tanto la forma en que oscila en respuesta a señales eléctricas.

«Las antenas tienen una frecuencia de resonancia natural para las señales eléctricas, que se define por su geometría, como un tono puro de audio en un sintonizador», dijo Wentzloff. «Al diseñar un circuito para monitorizar la señal en la antena y medir cuán cerca está de la resonancia natural de la antena, puede bloquear la señal transmitida a la frecuencia de resonancia de la antena.»

«Esta es la primera antena integrada que también sirve como su propia referencia. La radio en nuestro chip no precisa un ajuste externo. Una vez que se despliega una red de ellos, automáticamente se alinean en la misma frecuencia.» Los investigadores están ahora trabajando en la reducción del consumo de energía de la radio para que sea compatible con baterías a escala milimétrica.

Fuente: EurekAlert¡

Microordenador en formato «llave electrónica» USB

Un nuevo microordenador diseñado por David Braben, un desarrollador británico de juegos, permite aglutinar todas las prestaciones de un PC en un ordenador del tamaño de un pendrive USB. Su precio se estima del orden de 25 euros.

Este equipo, ha recibido el nombre de Raspberry Pi e incorpora como microprocesador un ARM11 comparable al que se encuentra en el primer iPhone. Con 128 Mb de memoria RAM, es necesario conectar a él un teclado, un ratón, un módem y una pantalla de televisor. Un puerto permite añadir una tarjeta de memoria y algunas extensiones, como una cámara de fotos. El sistema operativo no puede ser Windows, sino una distribución de Linux como Ubuntu.

Fuente: Fundación Raspberry Pi

autobus las palmas aeropuerto cetona de frambuesa